アナログシンセの VCO ブロック (41) -- 温度補償回路(7)

3.3 V 動作の VCO 回路の次の段階として、通常は温度係数 +3300 ppm/℃ の抵抗 (TEMPCO) を使うオクターブ・スパンの温度補償を、TEMPCO を使わずにトランジスタ・アレイ内の差動ペアを利用して行う回路を考えています。

まだ回路は組んでいませんが、LTspice シミュレーションを試してみました。

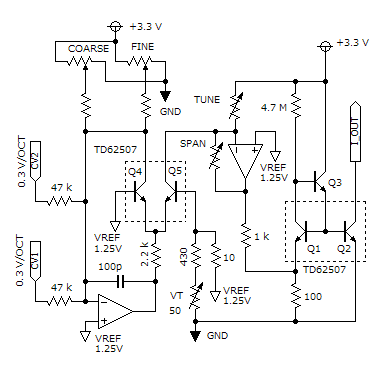

回路図を下に示します。

Q1、Q2 のアンチログ回路と同一のパッケージ内の Q4、Q5 を使って、絶対温度に比例する CV を作り出します。

2009 年 9 月 6 日付けの記事

http://d.hatena.ne.jp/pcm1723/20090906/1252251837

のところで述べたように、自然対数の底 e = 2.718281828... として、温度補償範囲の中心で差動ペアのコレクタ電流比が 1 : 1/e になるような温度に依存しない一定値のオフセット電圧をベース間に加えると、1/e の方の電流は近似的に絶対温度に比例するようになります。

Q4、Q5 周辺の回路は、この目的のために構成されており、OP アンプは CV 入力のサミング・アンプ機能と、差動ペアの大きい電流を流す方のトランジスタ Q4 のコレクタ電流をコントロールする機能を兼用しています。

Q5 のベース側のトリマ抵抗は、動作温度範囲の中心の温度で差動ペア Q4、Q5 の電流比が 1 : 1/e になるように調整します。

回路図の中央付近にある OP アンプで、ベース結合アンチログ回路のエミッタ側に加える電圧に変換します。

Q1、Q2、Q3 は、おなじみのベース結合アンチログ回路です。

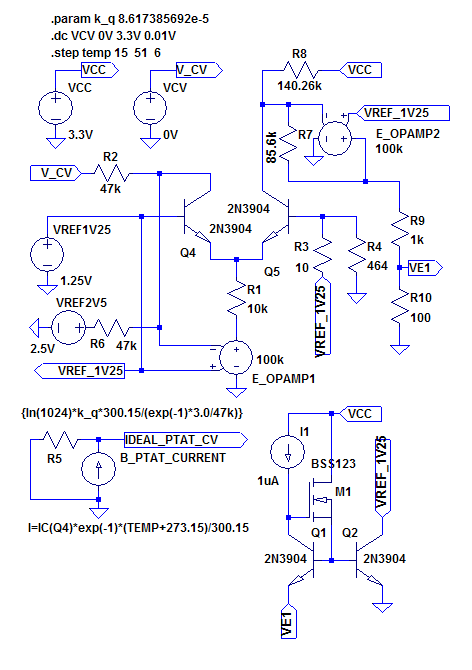

LTspice によるシミュレーションのための回路を下に示します。

温度補償回路を調べることが目的なので、ベース結合アンチログ回路については理想定電流源と N-ch MOSFET を使用してベース電流誤差を生じないようにしています。

また、OP アンプについては、電圧制御電圧源 (E エレメント) を使用した理想 OP アンプとなっています。

温度については、15 ℃ から 51 ℃ まで 6 ℃ ステップでスイープしています。

CV 電圧については、0.3 V/Oct として、0 〜 3 V で 10 オクターブをカバーします。

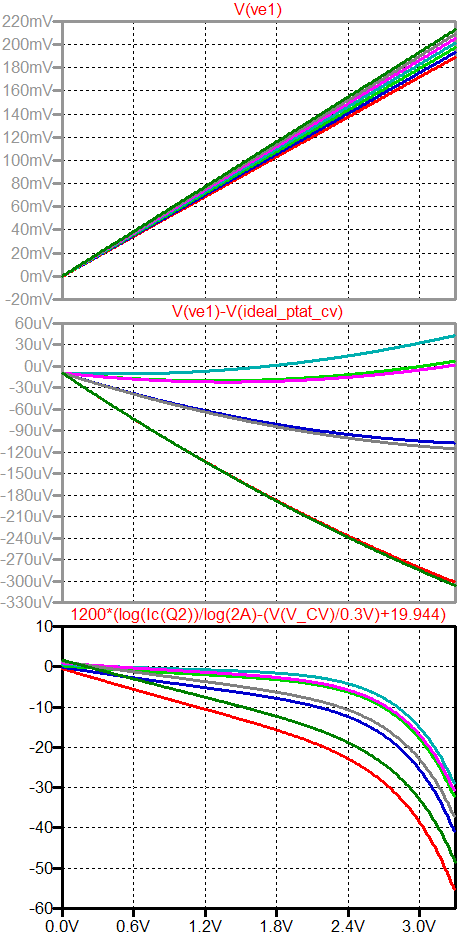

シミュレーション結果のプロットを下に示します。

各グラフの横軸は CV 入力の電圧値で、0 〜 3.3 V までを DC スイープしています。

温度をパラメタとして 15 ℃ から 6 ℃ ステップで 51 ℃ までプロットしています。 温度とトレースの色の対応は次の表のようになっています。

| 温度 (℃) |

色 |

|---|---|

| 51 | 暗い緑 |

| 45 | 灰 |

| 39 | マゼンタ |

| 33 | シアン |

| 27 | 緑 |

| 21 | 青 |

| 15 | 赤 |

一番上のグラフは、ベース結合アンチログ回路の Q1 のエミッタ電圧 (VE1) で、温度 27 ℃、CV = 3 V の時に約 180 mV になります。

真ん中のグラフは、VE1 の理論上の理想電圧からの誤差です。

このグラフ中の一番上のシアン色のトレースは、33 ℃ の場合で、その下に2本近接しているのが、緑 (27 ℃)、マゼンタ (39 ℃) 、その下の2本が、青 (21 ℃)、灰 (45 ℃)、さらにその下の2本が、赤 (15 ℃)、暗い緑 (51 ℃) です。

一番下のグラフは、アンチログ出力の電流値の理想値からの誤差をセント単位で表示したものです。

CV 電圧の高いほうで全体的に下がっているのはトランジスタの特性による誤差です。

各トレースと温度との対応は、真ん中のグラフと同様です。

このグラフからは、約 10 オクターブ幅、15 〜 51 ℃ の範囲で温度による誤差は 25 セント程度、温度範囲を 21 〜 45 ℃ に限るなら誤差は 10 セント程度になることが読み取れます。