PSoC5LP Prototyping Kit (1) --- KitProg

「PSoC5LP Prototyping Kit」を購入しました。

今回は「KitProg」部分と、電源回りの回路について述べたいと思います。

「KitProg」は「MiniProg3」の SWD プログラマ / SWD デバッグ・プローブ / USB-I2C ブリッジ相当の機能を実現したものです。

「MiniProg3」では SWD と USB-I2C ブリッジの機能との間でピンを共有しているので、プログラムを書き込む場合と、CapSense チューナーを使う場合とで接続を変更する必要があります。

一方、「KitProg」では SWD で使うピンと USB-I2C ブリッジで使うピンとが独立になっているので、プログラム書き込みのための SWD 接続と、 CapSense チューナーを使うための I2C 接続とは、それぞれつなぎっぱなしにしておけます。

また、「Bridge Control Panel」アプリケーションを使えば、I2C 接続されたデバイスとの間でインタラクティブにデータのやり取りができます。

さらに、「KitProg」では USB-UART ブリッジ機能 (仮想 COM ポート機能) も持っているので、ホスト PC 上のターミナル・ソフトを使ってターゲット・ボード側と UART を介してやり取りすることができます。

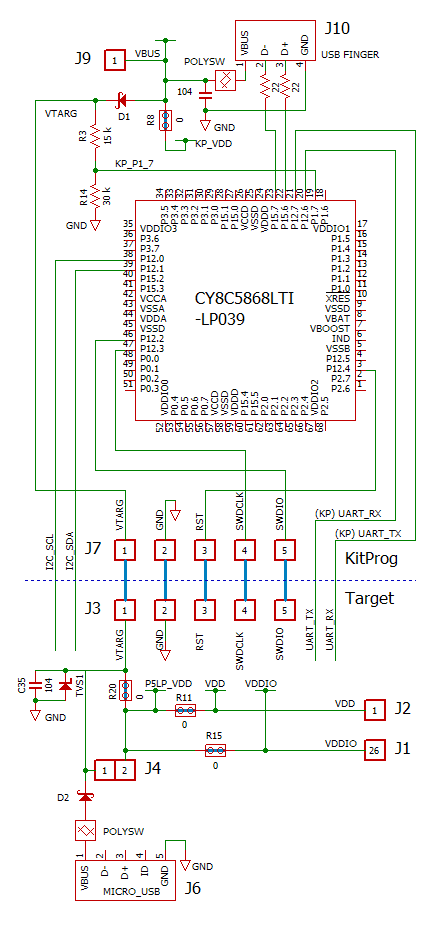

下に、KitProg 部分とターゲット部分の主に電源回りの回路を示します。

KitProg とターゲットとの間のスリット部分のシルク印刷では、5 本の SWD 接続しかないように見えますが、実際には、上の図のように 9 本の配線が通っていて、配線を追加する作業をしなくても、あらかじめ USB-UART ブリッジ機能、USB-I2C ブリッジ機能が利用可能になっています。

KitProg 部を切り離すと、SWD 接続だけでなく、他の 4 本の接続も切られてしまうので、もとの状態を回復するには J9 に引き出されている UART_TX / UART_RX / I2C_SDA / I2C_SCL 信号とターゲット側との配線の追加を行なう必要があります。

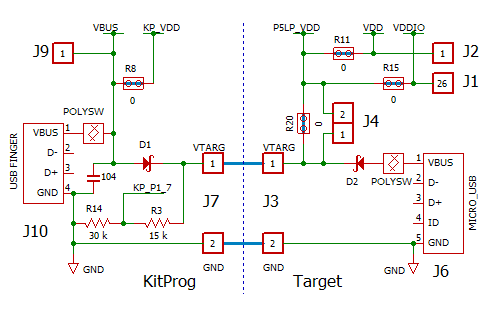

デフォルトの設定での、KitProg 部とターゲット部との電源回りの回路を下に示します。

この設定では、KitProg 側の USB フィンガー (PCB 上に形成された電極) に接続された USB VBUS からのターゲット側への電源供給、あるいはターゲット側の micro USB B-レセプタクルに接続された USB VBUS からの電源供給が可能です。

いずれの場合も、公称 5 V の VBUS 電圧からショットキ・ダイオードの VF 1 個分の電圧降下を差し引いた電圧がターゲット部の VDD として VTARG 端子に印加されます。

したがって、ターゲット部は 4.数 V の電圧で動作することになり、電圧レベル変換回路を挟まない限り基本的には外部回路も同電圧の VDD で動作させなければなりません。

ターゲット部を 3.3 V で動作させるには、ボードの改造および外部回路が必要です。

KitProg 部は USB フィンガーからの VBUS でのみ動作し、ターゲット側の USB のみつながっている場合には、KitProg 側には電源が供給されず、動作しません。

SWD 信号や UART / I2C の信号はターゲット側に接続されっぱなしですが、それらの信号は GPIO (General Purpose I/O) ではなく、SIO (Special I/O) ポートに接続されており、電源オフの場合には負荷に対してはインピーダンス無限大となって、ターゲット側には悪影響を及ぼしません。

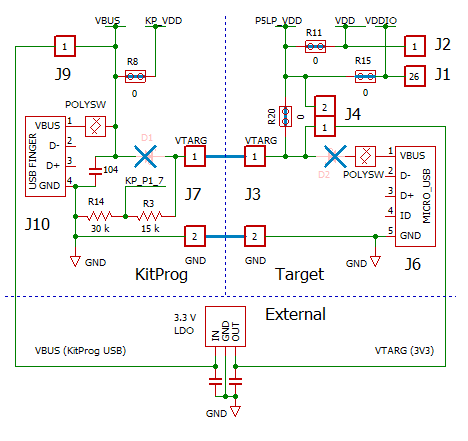

ターゲット部を 3.3 V で動かしたい場合で、電源供給は KitProg 側の USB のみで、ターゲット側の USB からは電源供給しない方針では、たとえば次の図のようになります。

まず、ショットキ・ダイオード D1、D2 を外して、いずれの USB からも VBUS 5 V が直接 VARG に流れ込むのを防ぎます。

KitProg 側の J9 に引き出されている VBUS 5V から外部のレギュレータにより 3.3 V を作り出し、VTARG に戻します。

スリット部の VTARG のランドは J1、J2 などの 100 mil グリッドに微妙に乗っていないので、100 mil グリッドに乗っている J4 の 1 番ピンに 3.3 V を接続します。

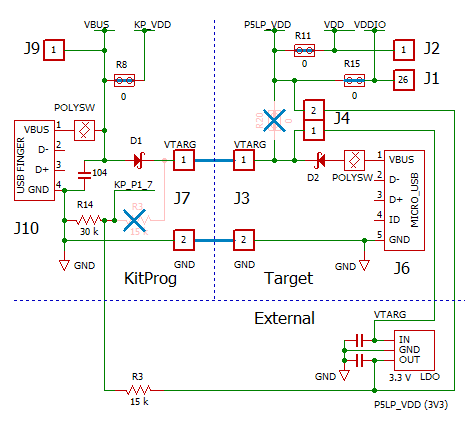

3.3 V 駆動でもデフォルトのように両方の USB からの電源供給が可能にするためには、たとえば次のような構成にします。

この場合、VTARG をターゲットに対する直接の電源とはせず、KitProg 側とターゲット側との USB VBUS を「合成」するノードとして扱うために、R20 の 0 Ω 抵抗を外してオープンにします。

R20 と J4 の本来の目的は、ターゲットの IDD を測定するために一時的に電源ラインをカットして電流計を接続するためのものです。

それを恒久的に分離し、J4 の 1 番ピンと 2 番ピンの間に 3.3 V レギュレータを接続してターゲット側の電源電圧 P5LP_VDD として 3.3 V が供給されるようにします。

KitProg 側では VTARG 電圧をモニタして、ターゲット側の電源電圧に合わせて SIO 出力ピンの「H」レベル電圧を調整しているので、その電圧モニタ経路も変更する必要があります。

R3 の 15 kΩ を外して、VTARG との接続を切り、新たに 15 kΩ の抵抗を介してターゲット側の P5LP_VDD と接続します。

上の図では、この接続を外部で行なうような表現になっていますが、KitProg 部を切り離さず一体化した状態のままで使用する前提なら、この接続は PSoC5LP Prototyping Kit ボード上で行なうことができます。