FPGA 版 FM 音源 (48) -- YMF297 (OPN3/OPL3) 測定 (13) -- EG パラメタ・レジスタ

今回の小ネタは、OPL3 の EG パラメタ (AR/DR/RR) の値が有効になる (参照される) タイミングについてです。

結論から言えば、アタック/ディケイ/リリースで、その状態に対応するレート・レジスタ AR/DR/RR が選択されている限り、ラッチされることはなく常に素通しで、ホスト・マイコンがそのレジスタの値を書き換えるとリアルタイムに出力に反映されます。

サステイン・レベル (SL) に関しては、サステイン状態への遷移の判断に使われるだけで、いったんサステイン状態に進むと、SL の値を変更しても EG の状態は変化しません。

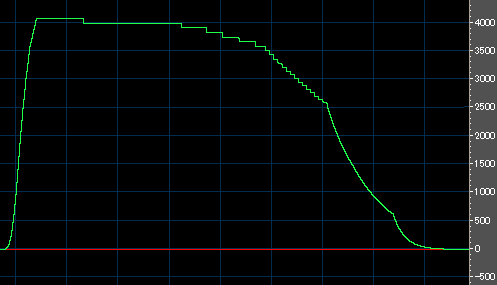

EG がリリース状態になってから遂次 RR を減衰が早くなるように書き換えた場合の、実チップの EG 出力のキャプチャ結果を下に示します。

「湾曲」した「折れ線」状態になっていますが、「湾曲」はリリースがエクスポネンシャルで変化するためであり、「折れ線」になるのは RR の数値を増やした結果が素通しでリアルタイムに反映されているためです。

これは、パイプラインおよび時分割多重 (タイム・スロット) 方式で 1 組のオペレータ・ハードウェアを多重化して利用する場合にオペレータごとに必要となる内部変数を減らすためと思われます。

たとえば、フェーズ・アキュムレータは発音チャネルごとに、EG アキュムレータおよび EG ステートマシン変数はオペレータごとに必要になります。

EG パラメタ・レジスタを何かのタイミングでラッチしてから利用すると、そのラッチした値を内部変数として保存する必要が生じ、ハードウェア量の増加を招きます。

ソフトウェアでは特に意図したものでない限り、そのレート・レジスタが有効な状態では値を変更しないという「お約束」にしておけば、特にハードウェアで値をラッチしておく必要もありません。