FPGA 版 FM 音源 (57) -- YMF297 (OPN3/OPL3) 測定 (23) -- FPGA 版 EG (1)

EG 部分を Verilog HDL で記述し、Altera (無印) Cyclone (EP1C3T100C8) 上にインプリメントしました。 (具体的には CQ 出版「デザインウェーブマガジン」 2003 年 10 月号付属基板)

開発環境としては、

- Quartus II Version 11.0 sp1 Web Edition

- ModelSim-ALTERA Starter Edition 6.6d

という古いものを使っています。 これ以降のバージョンでは、無印 Cyclone のサポートが打ち切られているためです。

EG モジュールを 4 つのサブモジュールに分割して記述しています。 それぞれを単独でコンパイルした場合のロジック・エレメント (LE) 使用量の表を下に示します。

| モジュール名 | LE 使用量 | 説明 |

|---|---|---|

| opl3_EG_psc | 52 | EG クロック・プリスケーラ |

| opl3_EG_acc | 54 | EG アキュムレータ部 |

| opl3_EG_ctrl | 48 | EG ステートマシン / コントロール部 |

| opl3_EG_mem | 12 | EG スロット・メモリ |

「opl3_EG_mem」は複数スロットを実現する場合の EG アキュムレータ / EG ステートマシンを記憶しておくためのメモリ (シフトレジスタ) で、スロット数 N_SLOT = 1 の場合は単なるゲートだけの回路となります。

N_SLOT = 2 の場合には 12 ビット幅、1 段のシフトレジスタとなりますが、LE 数としては 12 個で N_SLOT = 1 の場合と変化ありません。

N_SLOT = 4 以上 (シフトレジスタ 3 段以上) になると、論理合成ソフトウェアが推論して、埋め込み RAM である M4K セルを使用するメガファンクションに置き換えるため、段数が多くなっても LE 使用量としては 20 個程度に抑えられます。

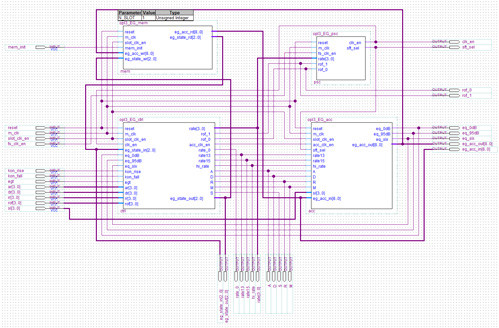

サブモジュールの接続の様子を回路図で表現したものを下に示します。 (図をクリックすると拡大します)

この図ではシミュレーションのために、サブモジュール間だけでやりとりされている信号も全て外部に引き出していますが、必要な信号だけを引き出した回路全体での LE 使用量は 153 個となります。

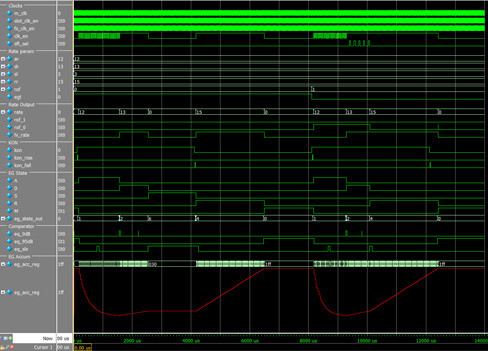

ModelSim によるシミュレーション結果を下に示します。 (図をクリックすると拡大します)

一番下の赤色のトレースは EG アキュムレータの値を「アナログ信号」として表示したものです。

「減衰量」なので、値が大きいほど減衰が大きく、出力レベルとしては小さくなります。

前半は egt = 1 としてサステイン・タイプのエンベロープ、後半は egt = 0 としてパーカッシブ・タイプのエンベロープを発生させています。