VHDL

(コンピュータ)

【ぶいえっちでぃえる】

Very high-speed integrated circuit Hard-ware Description Languageの略らしい。

ハードウェアのロジックを記載する言語。これをVHDLコンパイラーにかけてゲートアレイを設計したり、ロジックを検証したりする。

人によっては、理解するのが難しい為、Very Hard unDerstand Language(とっても理解するのが大変な言語)とか、Very Hard Description Language (記載するのがとっても大変な言語) と言われる事がある。

プログラムのようにロジックを記載してゲートアレイを設計出来るとハードウェアエンジニアが興味を持ち、ソフトウェアエンジニアもこれでハードも扱えると興味を持つが、ハードウェアエンジニアは記載言語がわからず挫折し、ソフトウェアエンジニアはハードウェアの概念がわからず挫折するという問題を秘めている。

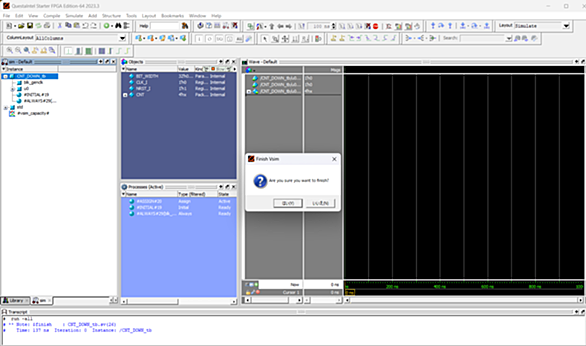

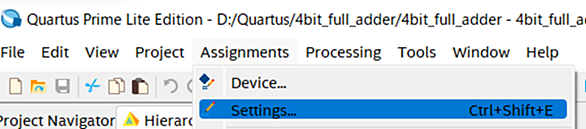

現在、多くの FPGA メーカーがフリーで使える開発環境を提供し、アマチュアが自作のCPUを設計出来る環境が出来ている。

しかし、実際に設計を行うには多くのノウハウが必要となる。

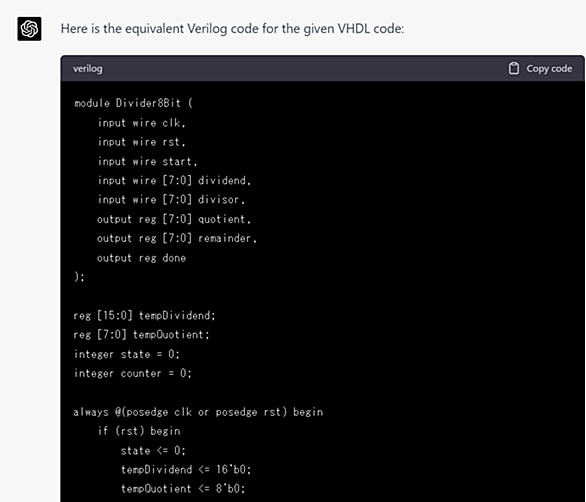

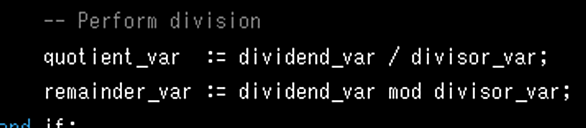

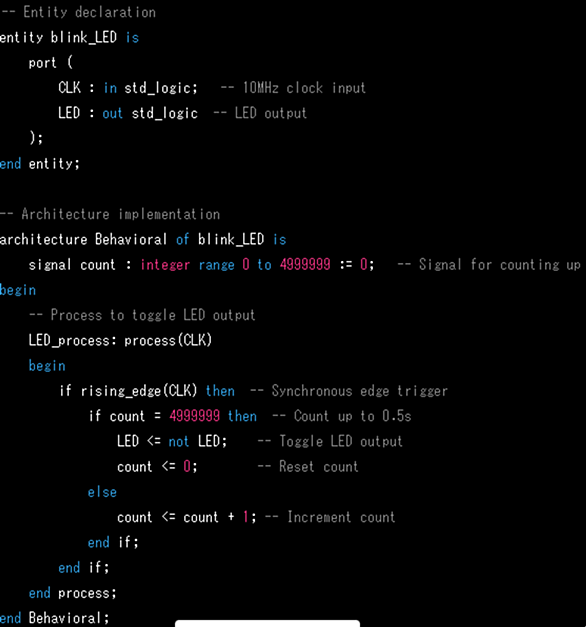

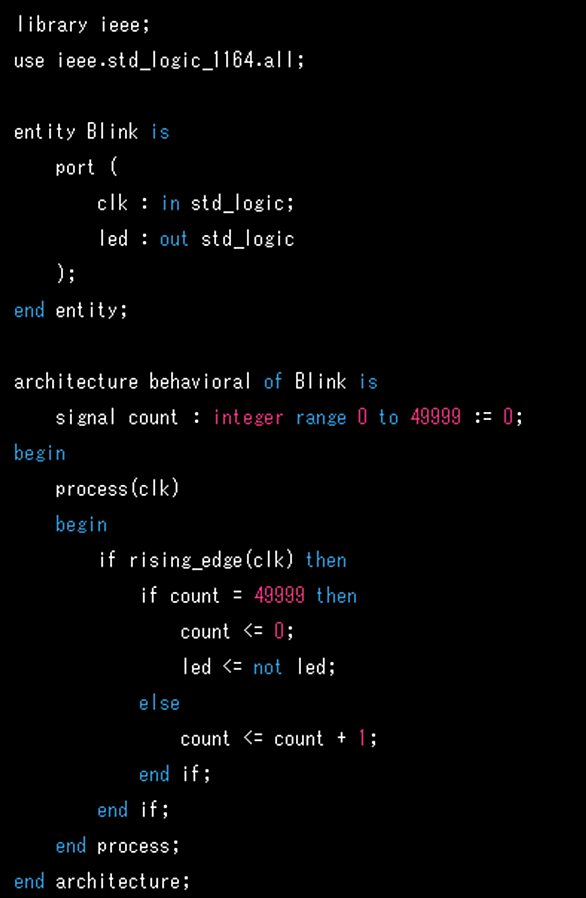

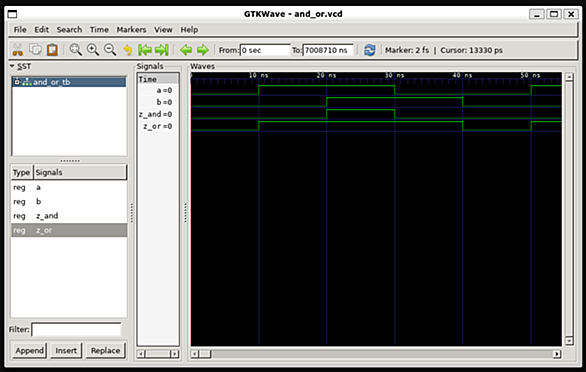

こんな感じで記載する。雰囲気はAdaに近い

library ieee; use ieee.std_logic_1164.all; entity example_ent is port( A : in std_logic; B : in std_logic; Y : out std_logic); end; architecture rtl of example_ent is begin Y <= A and B; end rtl;